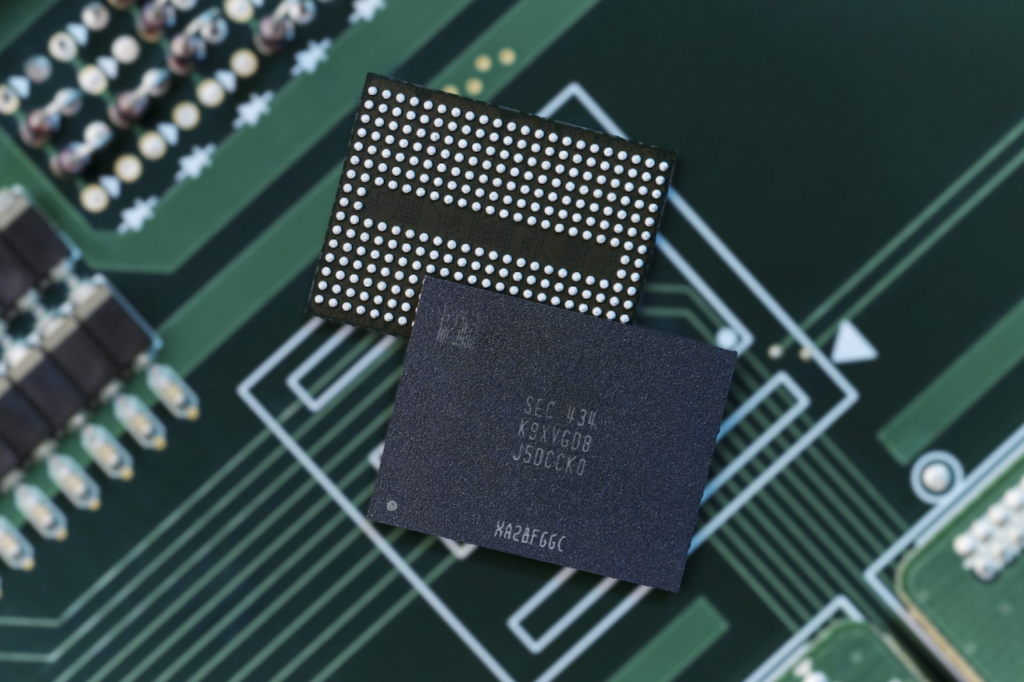

سامسونگ در حال توسعه تراشههای حافظه V-NAND با ۴۰۰ لایه است

سامسونگ در حال کار روی تراشههای حافظه V-NAND با ۴۰۰ لایه است که با استفاده از فناوری اتصال عمودی، ظرفیت ذخیرهسازی بیشتری ارائه خواهند داد. به گزارش تکناک، سامسونگ اعلام کرد که نسل جدید تراشههای حافظه V-NAND با ۴۰۰ لایه بهزودی عرضه خواهد شد. این فناوری پیشرفته میتواند حجم بیشتری از دادهها را ذخیره کند […] نوشته سامسونگ در حال توسعه تراشههای حافظه V-NAND با ۴۰۰ لایه است اولین بار در تک ناک. پدیدار شد.

سامسونگ در حال کار روی تراشههای حافظه V-NAND با ۴۰۰ لایه است که با استفاده از فناوری اتصال عمودی، ظرفیت ذخیرهسازی بیشتری ارائه خواهند داد.

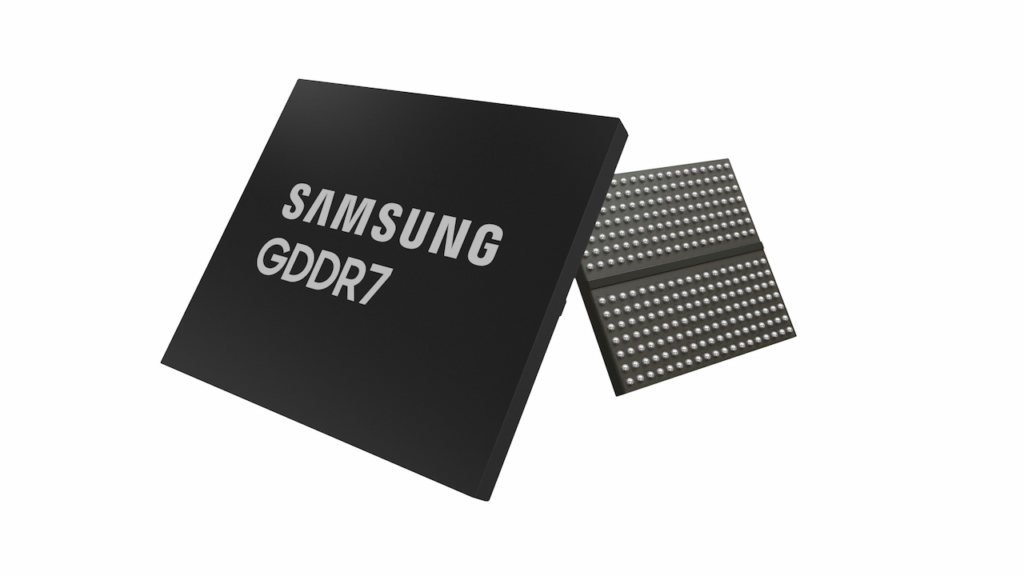

به گزارش تکناک، سامسونگ اعلام کرد که نسل جدید تراشههای حافظه V-NAND با ۴۰۰ لایه بهزودی عرضه خواهد شد. این فناوری پیشرفته میتواند حجم بیشتری از دادهها را ذخیره کند و بهدلیل قابلیت اطمینان بیشتر، گزینه مناسبی برای راهحلهای ذخیرهسازی آینده خواهد بود.

Wccftech مینویسد که شرکت سامسونگ قصد دارد تا با افزایش تعداد سلولهای حافظه در نسل جدید به حدود ۱۰۰۰ لایه در آینده برسد. این هدف در حالی مطرح میشود که سامسونگ یک ماه پیش، تولید انبوه V-NAND نسل نهم QLC را با هدف بهبود عملکرد و ظرفیت ذخیرهسازی و اطمینان راهحلهای ذخیرهسازی آغاز کرده است. براساس گزارشهای Korean Economic Daily، سامسونگ با بهرهگیری از فناوری جدید V-NAND بهدنبال دستیابی به کارایی بالاتری است.

سامسونگ برای دستیابی به این هدف، قرار است نسل دهم V-NAND خود را در سال ۲۰۲۶ عرضه کند. این نسل به پیکربندی ۴۰۰ لایه مجهز خواهد بود که در مقایسه با V-NAND نسل نهم، افزایشی معادل ۱۲۰ لایه یا حدود ۴۳ درصد را نشان میدهد؛ افزایشی که بسیار بیشتر از فاصله میان لایههای V-NAND نسل هشتم و نهم (۲۳۶ و ۲۸۰ لایه) است.

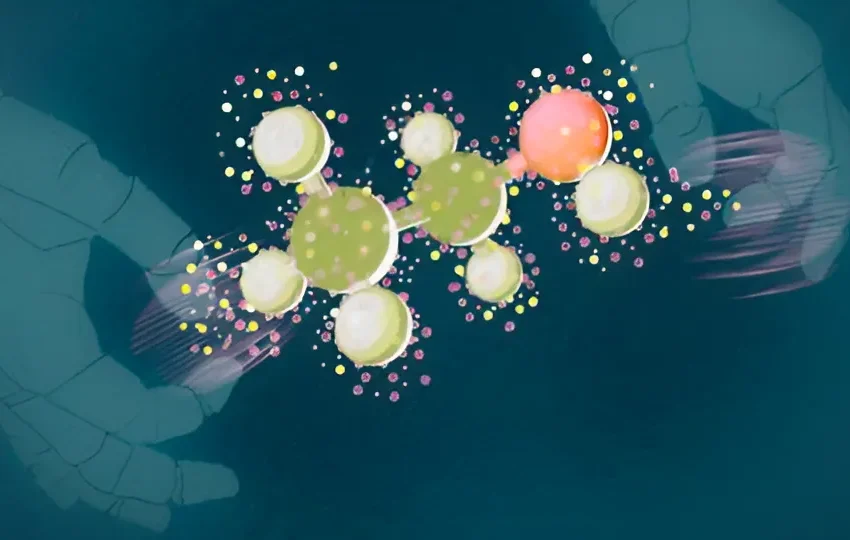

سامسونگ برای دستیابی به چنین ساختاری، از فناوری Bonding Vertical (BV) NAND بهره خواهد برد که با طراحی کنونی CoP (مدار در پیرامون) متفاوت است. در طراحی CoP، مدارهای پیرامونی در بالای پشته حافظه قرار میگیرند؛ اما روش پیوند عمودی با تولید جداگانه مدارهای ذخیرهسازی و پیرامونی آغاز شده و سپس این مدارها به صورت عمودی پیوند میخورند.

این روش جدید نهتنها ظرفیت بیشتری فراهم میکند؛ بلکه احتمال آسیب به مدارها طی فرایند چیدن لایهها را کاهش میدهد. پیوند عمودی مشابه روش Xtacking شرکت YMTC و CBA (آرایه پیوند CMOS) شرکت Kioxia-Western Digital است که با این روش میتوان به چگالی بیت حدود ۶۰ درصد بیشتر دست یافت و ظرفیت ذخیرهسازی را در همان فضای موجود بهشدت افزایش داد.

سامسونگ قصد دارد تا سال ۲۰۲۷، تعداد لایههای V-NAND را به هزار لایه برساند؛ اما احتمالاً این هدف در نسل یازدهم V-NAND محقق خواهد شد. دستیابی به این فناوری میتواند نرخ I/O را تا ۵۰ درصد بهبود بخشد.

در بخش DRAM نیز، سامسونگ اعلام کرده است که تا سال ۲۰۲۷ نسخهای سریعتر و پیشرفتهتر از DRAM عرضه خواهد کرد. این محصول با فناوری کمتر از ۱۰ نانومتر (0a nm) ساخته میشود و از فناوری VCT (ترانزیستور کانال عمودی) برای افزایش ظرفیت حافظه استفاده خواهد کرد. فناوری VCT به سامسونگ امکان میدهد تا DRAM سهبعدی طراحی کند و با چینش عمودی ترانزیستورها، تداخل سلولهای مجاور را کاهش دهد.

روند توسعه DRAM با تولید DRAM برپایه nm 1c در سال ۲۰۲۵ آغاز خواهد و پساز آن، در سالهای ۲۰۲۶ و ۲۰۲۷ به ترتیب DRAM 1d nm و DRAM 0a nm عرضه خواهند شد.

نوشته سامسونگ در حال توسعه تراشههای حافظه V-NAND با ۴۰۰ لایه است اولین بار در تک ناک. پدیدار شد.

واکنش شما چیست؟

![ایلان ماسک حالا بهترین بازیکن Diablo 4 در جهان است [تماشا کنید]](https://static.digiato.com/digiato/2024/11/Elon-Musk-Diablo-4.jpg)